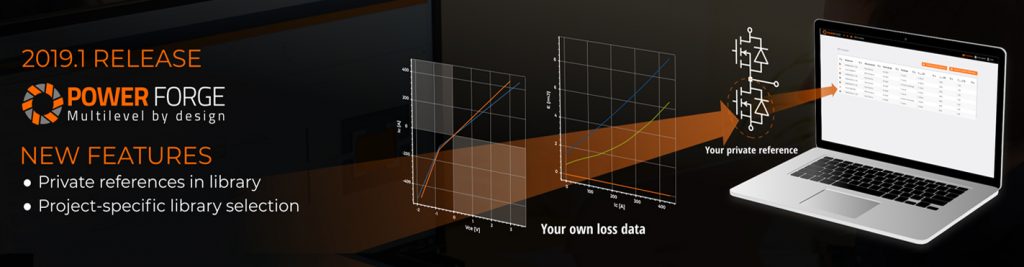

● Private references in library

- Users can now create private discrete and module (leg, T-type, NPC) library references, providing loss data in Plecs XML format (‘Table only’ supported, no formula)

- Users can now create private semiconductor package footprints (they can be used for abovementioned discretes & modules)

- Private library references are shared among members of an organization

- Private library references can be used interchangeably with public references in designs

● Project-specific library selection

- Each project’s owner can select a freely-configurable subset of all available library references

- Only selected library references will be used in the project’s designs